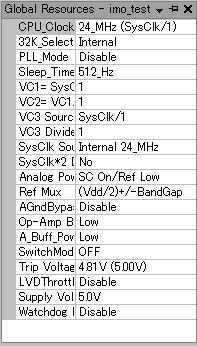

PSoCには24MHzの内部クロックがあり、外付発振器なしに最高24MHzで駆動させることができます。

TRM(Technical Reference Manual)のP105によりますと、

the accuracy of the internal 24/48 MHz clocks will be +/-2.5% over temperature variation and two voltage ranges (3.3V ± 0.3V and 5.0V ± 0.25%).

となってまして、電源電圧3.3V ± 0.3V と 5.0V± 0.25%において精度が+/-2.5% になっております。

この精度が実際にはどの程度か実験しました。

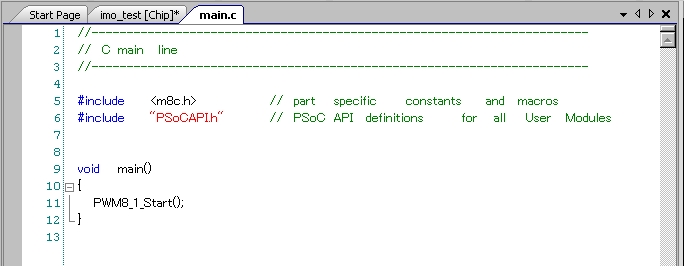

まず、PSoC Designer5.0 から新規作成です。

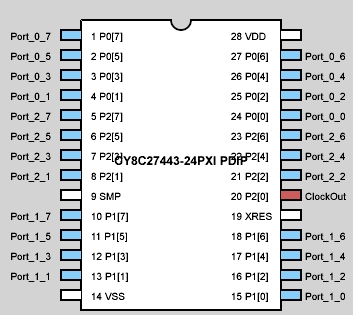

プロジェクトファイル CY8C27443-24PXI

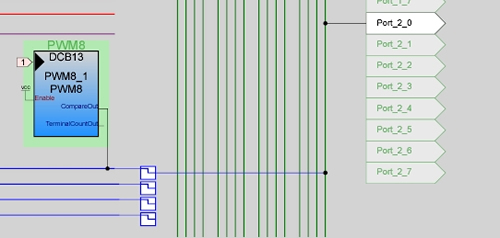

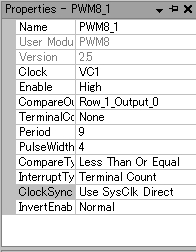

【説明】 まっ、説明することもないとおもいますが、sysclk(24MHz)をPWM8にて 1/10 にしてPort2_0( 20ピン)に出力します。

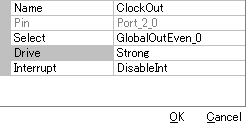

注1)[View] --> [Pinout] --> [+]P2[0] --> [Drive] が Strong になっている事。

注2)[PWM8_1] --> [ClockSync] には Use SysClk Direct を選択する事。

ClockOut(20pin) |

SysClk |

備考 |

|

defalt |

2.439MHz |

24.39MHz |

Tektronix2432A [Vcc] 5.10V [temp] 28.8℃ |

(24.39(MHz)/24(MHz)×100) - 100 = 1.625(%)

となり、TRM に書かれてあるようになりました。

・・・・・っが、納得いきません!

TRM をよく読みますと、P106に 「8.3.1 Trimming the IMO」の記載があります。

8.3.1 Trimming the IMO An 8-bit register (IMO_TR) is used to trim the IMO. Bit 0 is the LSB and bit 7 is the MSB. The trim step size is approxi- mately 80 kHz. A factory trim setting is loaded into the IMO_TR register at boot time for 5V +/- 0.25V operation, except for the CY7C603xx, which is 3.3V +/- 0.25V. For operation in the voltage ranges of 3.3V +/-0.3V and 2.7V +/- 0.3V, user code must modify the contents of this register with values stored in Flash bank 0 as shown in Table 3-11 on page 75. This is done with a Table Read command to the Supervisory ROM. |

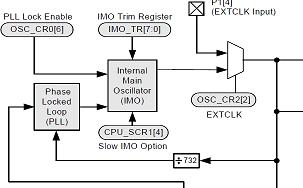

内部ブロック図です。P444より

[IMO_TR]は工場出荷時にセッティングされているようで、ちょっといじってみます。

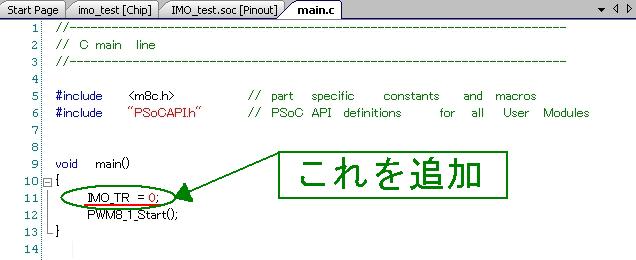

さきほどのプロジェクトファイルの main() 内に

IMO_TR = 0;

を追加してみます。下記が結果です。

ClockOut(20pin) |

SysClk |

備考 |

|

IMO_TR=0 |

1.455MHz |

14.55MHz |

Tektronix2432A [Vcc] 5.10V [temp] 28.8℃ |

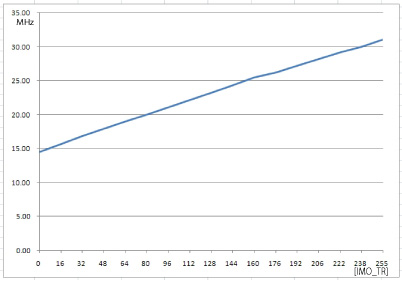

IMO_TR を変更してみました。

IMO_TR

|

ClockOut(20pin) |

SysClk |

備考 |

|

0x00 |

1.455MHz |

14.55MHz |

Tektronix2432A [Vcc] 5.10V [temp] 28.8℃ |

0x10 |

1.575MHz |

15.75MHz |

|

0x20 |

1.689MHz |

16.89MHz |

|

0x30 |

1.801MHz |

18.01MHz |

|

0x40 |

1.904MHz |

19.04MHz |

|

0x50 |

2.008MHz |

20.08MHz |

|

0x60 |

2.114MHz |

21.14MHz |

|

0x70 |

2.223MHz |

22.23MHz |

|

0x80 |

2.325MHz |

23.25MHz |

|

0x90 |

2.433MHz |

24.33MHz |

|

0xA0 |

2.531MHz |

25.51MHz |

|

0xB0 |

2.624MHz |

26.24MHz |

|

0xC0 |

2.721MHz |

27.21MHz |

|

0xD0 |

2.820MHz |

28.20MHz |

|

0xE0 |

2.918MHz |

29.18MHz |

|

0xF0 |

3.006MHz |

30.06MHz |

|

0xFF |

3.111MHz |

31.11MHz |

【結果】

IMO_TR = 0x8A にてPWM8より2.401MHzとなりました。結果24.01MHzにて動いているわけです。

(24.01(MHz)/24(MHz)×100) - 100 = 0.0416(%)

これ位ならなんとかなりますね!

プロジェクトファイル なお、使用コンパイラは HI-TECH C PL9.61,PSoC Designer 5.0です。

【作成日】2008年7月31日

※Cypress、サイプレス社のロゴおよびPSoCはサイプレス セミコンダクタ社の登録商標であり、

PSoC Creator,PSoC Designer、PSoC Express,および Programmable System-on-Chip はサイプレス セミコンダクタ社の商標です。

Copyright (C) 2015 えとせとら All Rights Reserved